ISSN: 2251-8843

# Efficient Code Converter Circuits Design and Implementation in QCA Technology

A. Mallaiah<sup>1</sup>, G. N. Swamy<sup>2</sup>, K. Padmapriya<sup>3</sup>

<sup>1</sup>Research Scholar, JNTUA, Anthapuramu, A. P., India

<sup>2</sup>Department of EI&E, VR Siddhartha Engineering College, Vijayawada, A. P., India

<sup>3</sup>Department of ECE, JNTUK, Kakinada, A. P., India

(<sup>1</sup>malli797@gmail.com)

Abstract- In this paper, we proposed the realization of binary to gray code & gray to the binary code converter using Quantum dot Cellular Automata (QCA). The QCA converters used in a Nano electronic circuits and communication applications. The method behind used is based on the interaction of electrons with the quantum dots and utilizes the quantum phenomena. The quantum method may be shown highly complex in next generation integrated circuits. These converters modeled with QCA design software. We have calculated designed comparator area  $0.06~\mu m^2$  with 45 cells for binary to gray code converts and  $0.08~\mu m^2$  area with 55 cells of gray to binary code converter for 4 bit and also designed these converters 8 bit,16 bit, 32 bits.

Keywords-Code Converter, Circuit, QCA, Binary, Gray Code

#### I. INTRODUCTION

CMOS technology is accomplishing its physical limits while at the same time power consumptions and size of circuits are increasing at an alarming pace [1-4]. In order to reduce these problems in CMOS technology, different new technologies suggested in recent years [5],[6]. Present CMOS technology facing problems delay, power consumption, the area is the major matters. The problems generated by that technology can overcome by one of the new and emerging technology quantum dot cellular automata (QCA). The main characters of this technology are logical states representation not in terms of voltage levels alternately represented in terms of logic cells. OCA technology uses less device coulomb interaction to perform the calculation. In IC technology transfer of electrons named as current flow in the devices but in OCA does not involve any transfer of electron in the gates and circuits only charge transformation that's why extremely low power computing even below regular temperature 300° kelvin. QCA Designer is the one of layout tool for Quantum-dot cellular automata (QCA). The QCA logic gates and QCA circuits are carried out by a group of basic parts are named as QCA cells.

## II. QCA DESIGNER BASICS

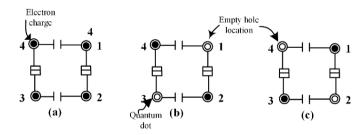

A cell is a nanometer structure like a square that has four quantum dots and these quantum dots are placed in four corners of the cells. The quantum dot is a nanometer sized conductive materials which walled by a nonconductive material [7]. So this structure could drain the electrons in threedimensional space and if an electron comes into a quantum dot, without enough electrical potential electrons cannot escape from the quantum dot. By injecting two additional electrons into a QCA cell by applying an external potential force, these electrons have might tunneling between quantum dots. In these quantum dots has a polarity and these polarities represent the electrical charge of the quantum dot. External inserted two electrons in the cell have columbic interaction two different possibilities of arrangements named as negative polarity and positive polarity represents the binary 0 and binary 1 for the cell. QCA cell four quantum dots together using tunnel junctions and we can control the external input supply of the tunnel junction to lock the position of charge or enable signal that allows controlling the state of QCA cells to binary 0 or binary 1 position [8-10].

Figure 1. Logic states representation of QCA cell (a) Electrons filled with four corners of quantum dot (b) logic 0 representation (c) QCA cell logic 1 representation

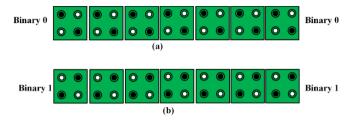

Figure 2. Representation of QCA wire (a) Binary 0 propagation (b) Binary 1 propagation

The arrangement of QCA cells side by side shown in figure 2 (a) and (b) work as a QCA wire. By applying binary 0 or binary 1 at one side of the wire another side of the wire same logic levels reached hence this arrangement of QCA cells works as QCA wire.

Three different simulation engines are available in latest version 2.0.3 of QCA design software.

- 1. Digital Logic Simulator: which conceives the quantum cell to be either fully polarized or zero polarization also known as a bistable simulator.

- 2. Nonlinear approximation engine: which uses the nonlinear cell-to-cell response function and stable state condition of the quantum cell in a QCA design.

- 3. Two state Hamiltonian: which utilizes quantum mechanical model approximation.

The main troubles in the design of simulation engine more accurately need but very less practical observation of results less available in QCA design if it is constructed with more number of cells [11]. However different experimental groups developed small QCA systems for proof of concept experiments [12]. As a result, the objective of this cause is to furnish need of future research work on QCA designs.

# III. PROPOSED DESIGNING APPROACH

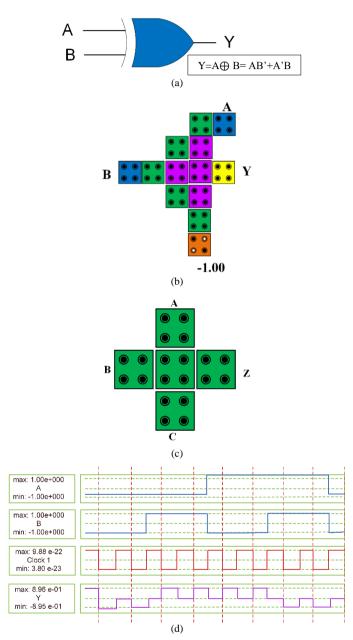

The primary making block of QCA circuit is XOR gate is implemented with a minimum number of cells equal to 12. In the previous work designed code converters [13-16] implemented with the 3 input majority gate with other logic gates, we are going to design approach employed the two input XOR gate with less number of cells and show output timing graph in 3(d). In this approach, some other functional combinational circuits implemented but here presented only code converters.

### A. Exclusive OR gate

As shown in figure 3, input of XOR gate labeled as the A&B output of the gate labeled as Y.

Most of the QCA layouts are designed using majority gate (or) voter (MV). This gate is a fundamental logic unit of most of QCA designs. There are different types of majority gate such as 3 input, 5 input, and 7 input, majority gate [17]. But 3 input majority gate is popular gate easy to implement and fundamental logical gates can be designed with 5 cells.

Z=MV(ABC)=AB+BC+CA, Whereas A B C are inputs of majority gate and Z as the output of majority gate.

Figure 3. (a) Exclusive OR gate symbol, (b) XOR gate QCA design, (c) Majority voter QCA design, (d) Output response of XOR gate

# B. Code converter

Two electronic systems using different codes for same data in that situation code converter are useful. Thus a code converter is a logic circuit whose inputs are bit patterns representing numbers in one code and whose output is the corresponding representation in a different code. Both electronic systems use different binary codes but code

converter generates compatible binary code to both systems. Normally code converters output has many numbers of output circuits.

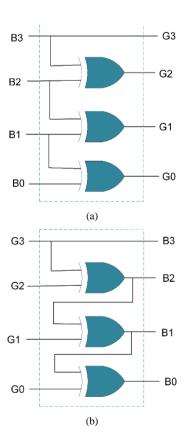

## 1) Binary to Gray code converter

The binary to gray code converter has a regular structure designed using XOR gates, a 4 bit binary to gray code converter circuit is a 4-bit binary input and 4-bit gray output bits all are valid output combinations here no don't care shown in the figure 4(a) [18][19][21]. In this paper, we are presented 4- bit binary to gray code QCA layout shown in figure 5, designed with minimum area. It utilizes a 3 XOR gates and total area is  $0.06 \ \mu m^2$ .

The expression for the binary to gray code converter as

$G3=\sum m(8,9,10,11,12,13,14,15)$

$G2=\sum m(4,5,6,7,8,9,10,11)$

$G1=\sum m(2,3,4,5,10,11,12,13)$

$G0=\sum m(1,2,5,6,9,10,13,14)$

After simplification minimal expression for the outputs obtained

G3=B3

$G2 = B3 \oplus B2$

G1=B2\(\)B1

$G0 = B1 \oplus B0$

Figure 4. (a) Binary to Gray code converter Logic Circuit (b) Gray to Binary logic Circuit

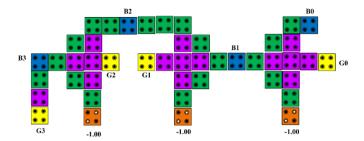

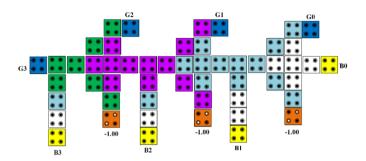

Figure 5. QCA Layout of Binary to Gray Code Converter

Figure 6. QCA Layout of Gray to Binary Converter

# 2) Gray to Binary code converter

Figure 4(b) shows a circuit diagram of 4-bit gray to binary code converter and figure 6 shows QCA layout of gray to binary converter. This 4-bit converter takes 3 clock cycles to convert and in general, it takes n-1 clock cycles to take conversion, as the number of bits increases gray to binary conversion time also increases. The following equation is used for a gray to binary code conversion.

B3=G3

B2=G3⊕G2

B1=B2⊕G1

B0=B1⊕G0

#### IV. SIMULATION RESULTS AND ANALYSIS REPORT

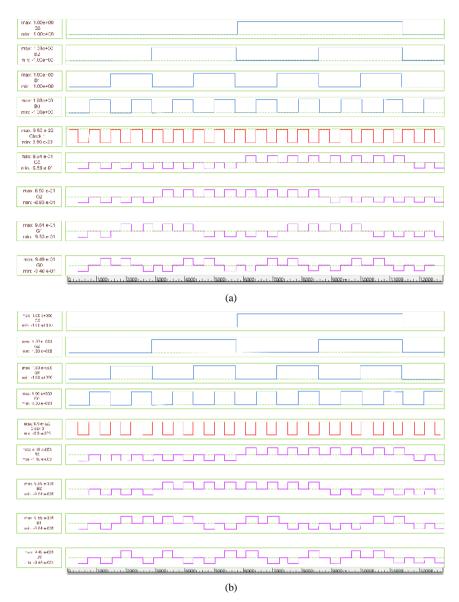

Simulation results of code converter shown in the 7 (a) & (b). In this proposed code converters design utilized basic gate used XOR gate designed with a minimum number of cells and zero majority gates. We have designed the code converters of 4-bit, 8-bit, 16-bit and 32 bit with less area and less number of cells. The binary to gray code converter and gray to binary converter QCA layout uses zero crossovers. The proposed binary to gray takes 2 clock phases for any number of bits, and it takes 0.06  $\mu m^2$  area with 45 numbers of cells with ½ clock delay for 4 bit binary to gray converter. Whereas gray to binary converter for 4-bit operation takes 0.08 µm<sup>2</sup>, with 55 cells, 1 clock phase taken. Remaining designed converters 8-bit, 16-bit and 32-bit details listed in the table 2. It is expected that the newly designed scheme for QCA of code converter introduced in this paper significant improvement in the Nano-electronic circuits and reduces area and delay of future QCA architectures.

International Journal of Science and Engineering Investigations, Volume 7, Issue 75, April 2018

Figure 7. Simulation results of proposed (a) Binary to Gray Code Converter (b) Gray to Binary Converter

TABLE I. AREA, OVERALL SIZE, NUMBER OF CELLS, DELAY RESULTS OF PROPOSED QCA CONVERTER

| Name of the Logic Circuit        |        | Area (nm)      | Overall size (µm) <sup>2</sup> | Cells | Delay (Clk) | Number of Clock Phases |

|----------------------------------|--------|----------------|--------------------------------|-------|-------------|------------------------|

| Binary to Gray Code<br>Converter | 4 bit  | 370.00x172.00  | 0.06                           | 45    | 1/2         | 2                      |

|                                  | 8 bit  | 873.88x175.88  | 0.15                           | 107   | 1/2         | 2                      |

|                                  | 16 bit | 1816.88x183.30 | 0.33                           | 227   | 1/2         | 2                      |

|                                  | 32 bit | 1939.00x340.89 | 0.66                           | 477   | 1/2         | 2                      |

| Gray to Binary Code<br>Converter | 4 bit  | 355.88x224.89  | 0.08                           | 55    | 1           | 4                      |

|                                  | 8 bit  | 755.88x224.89  | 0.17                           | 122   | 1           | 4                      |

|                                  | 16 bit | 919.39x404.89  | 0.37                           | 265   | 1           | 4                      |

|                                  | 32 bit | 991.35x784.89  | 0.78                           | 550   | 1           | 4                      |

## V. CONCLUSION

Majority gate is one of basic QCA gate with inverter gate together possible to design of XOR gate, AND & OR gate by applying one input of majority gate is -1 or 1 polarization to the majority gate. We designed modified majority gate work as a XOR gate or full adder with a minimum number of cells compared to earlier QCA layouts. These proposed circuits distinguish oneself earlier reported designs in terms of overall size, logic gate count, delay and number of cells. Moreover, the main advantage of the presented implementation is in a single layer with zero cross over the wiring. This research study can be carried to design the Quantum Cellular Automata layouts in Nano-electronic applications.

#### REFERENCES

- Schaller, Robert R. "Moore's law: past, present and future." Spectrum, IEEE 34, no. 6 (1997): 52-59.

- [2] Lent, Craig S., P. Douglas Tougaw, Wolfgang Porod, and Gary H. Bernstein. "Quantum cellular automata." In Nanotechnology, vol 4, no. 1 (1993): 49.

- [3] Niemier, Michael Thaddeus. "Designing digital systems in quantum cellular automata." PhD diss., University of Notre Dame, 2004.

- [4] Orlov, A. O., I. Amlani, G. H. Bernstein, C. S. Lent, and G. L. Snider. "Realization of a functional cell for quantum-dot cellular automata." Science 277, no. 5328 (1997): 928-930.

- [5] Tahoori, Mehdi Baradaran, Mariam Momenzadeh, Jing Huang, and Fabrizio Lombardi. "Defects and faults in quantum cellular automata at nano scale." In 22nd IEEE VLSI Test Symposium, 2004. Proceedings., pp. 291-296. IEEE, 2004.

- [6] Snider, Gregory L., Alexei O. Orlov, I. Amlani, X. Zuo, G. H. Bernstein, C. S. Lent, J. L. Merz, and W. Porod. "Quantum-dot cellular automata." Journal of Vacuum Science & Technology A 17, no. 4 (1999): 13941398.

- [7] S.Karthigai Lakshmi, G.Athisha. "Efficient design of logical structures and functions using nanotechnology based quantum dot cellular automata design." International Journal of Computer Applications, Vol. 3, No. 5, 2010 pp. 0975-8887.

- [8] Shahidinejad, Ali, and Ali Selamat. "Design of first adder/subtractor using quantum-dot cellular automata." In Advanced Materials Research, vol. 403, pp. 3392-3397. 2012.

- [9] V. A. Mardiris and I. G. Karafyllidis, "Design and simulation of modular 2 to 1 quantum-dot cellular automata (QCA) multiplexers"

- International Journal of Circuit Theory and Applications, vol. 38, no. 8, pp. 771–785, 2010.

- [10] A. Sarkar and D. Mukhopadhyay, "Improved quantum dot cellular automata 4: 1 multiplexer circuit unit," SOP Transactions on Nano-Technology, vol.1,no.1,pp.37–44,2014.

- [11] Firdous Ahmad, Peer Zahoor Ahmad, and G. Mohiud dinBhat. "Design and analysis of odd-and even-parity generators and checkers using Quantum-dot Cellular Automata (QCA)." In Computing for Sustainable Global Development (INDIACom), 2015 2nd International Conference on, pp. 187-194, 2015.

- [12] N. R. G, P. C. Srikanth, and P. Sharan, "A novel quantumdot cellular automata for parity bit generator and parity checker," *International Journal of Emerging Technology in Computer Science & Electronics*, 14, 2015.

- [13] Neeraj Kumar Misra, Subodh Wairya, Vinod Kumar Singh, "Optimized Approach for Reversible Code Converters Using Quantum-Dot Cellular Automata", In Proceedings of the 4th International Conference on Frontiers in Intelligent Computing: Theory and Applications (FICTA), Springer India, pp.367-378, 2016.

- [14] W. Liu, S. Srivastava, L. Lu, M. O'Neill, and E. Swartzlander Jr., "Are qca cryptographic circuits resistant to power analysis attack?" IEEE Transactions on Nanotechnology, vol. 11, pp. 1239–1251, 2012.

- [15] Graunke, C.R., Wheeler, D.I., Tougaw, D. and Will, J.D.: Implementation of a crossbar network using quantum-dot cellular automata. IEEE Trans. on Nanotechnology, Vol. 4(4), 435-440 (2005)

- [16] James C. ellenbogen, J.Christopher Love, "Architectures for molecular electronics computers: 1. Logic structures and an adder designed from molecular electronic diodes, Proceedings of the IEEE, March 2000, page 386-426.

- [17] Shamik Das and Matthew F. Bauwens, "Clocking Nanocircuits for Nanocomputers and other Nanoelectronic Systems", IEEE International Syposium on Nanoscale Architecture (NANOARCH 2007), Page 123-128

- [18] Adam C Cabe and shamik Das, "Performance simulation and analysis of a CMOS/Nano Hybrid Nanoprocessor systems", IEEE Nanotechnology, Vol. 20,no.16, 22 Apr 2009, Page 1-12

- [19] A. Chaudhary et al., "Fabricatable interconnect and molecular QCA circuits," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol.26, no. 11, pp. 1978–1991, Nov. 2007.

- [20] B. Bishnoi, M. Giridhar, B. Ghosh, and M. Nagaraju, "Ripple carry adder using five input majority gates," in Proc. IEEE Int. Conf. Electron. Devices Solid State Circuit, 2012, pp. 1–4.

- [21] S. Srivastava, A. Asthana, S. Bhanja and S. Sarkar, "QCAPro An error-power estimation tool for QCA circuit design," Circuits and Systems (ISCAS), 2011 IEEE International Symposium on, Rio de Janeiro, 2011, pp. 2377-2380.

www.IJSEI.com ISSN: 2251-8843 Paper ID: 77518-08